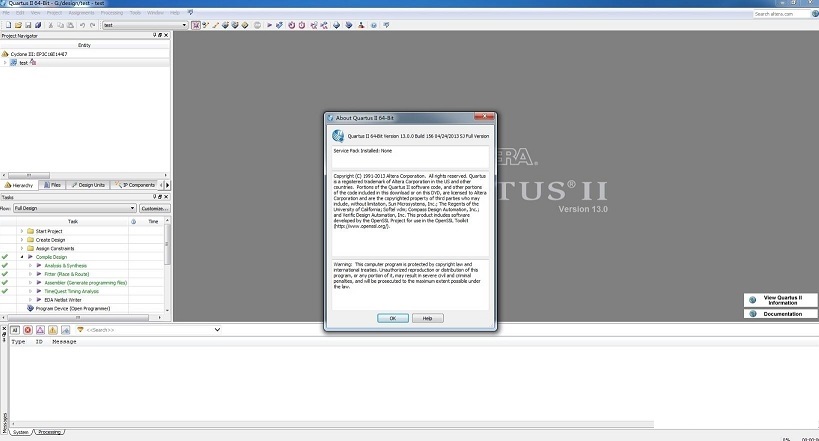

Qiartus13.1软件简介

Quartus II 是Altera公司的综合性PLD/FPGA开发软件,原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware 支持Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

Qiartus13.1功能介绍

1.自动定位编译错误;

2.高效的期间编程与验证工具;

3.功能强大的逻辑综合工具;

4.芯片(电路)平面布局连线编辑;

5.定时/时序分析与关键路径延时分析;

6.完备的电路功能仿真与时序逻辑仿真工具;

7.使用组合编译方式可一次完成整体设计流程;

8.可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析;

9.能生成第三方eda软件使用的VHDL网表文件和Verilog网表文件;

10.支持软件源文件的添加和创建,并将它们链接起来生成编程文件。

Qiartus13.1软件特点

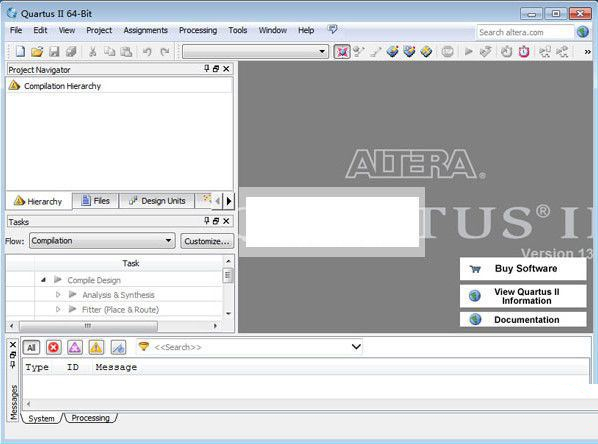

1.Altera Quartus II 作为一种可编程逻辑的设计环境, 由于其强大的设计能力和直观易用的接口,越来越受到数字系统设计者的欢迎。

2.Quartus II提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;芯片(电路)平面布局连线编辑等功能!

Qiartus13.1增强功能

高级设计流程

1、OpenCL的SDK为没有FPGA设计经验的软件编程人员打开了强大的并行FPGA加速设计新世界。

从代码到硬件实现,OpenCL并行编程模型提供了最快的方法。与其他硬件体系结构相比, FPGA的软件编程人员以极低的功耗实现了很高的性能。

2、Qsys系统集成工具提供?曰贏RM的Cyclone V SoC的扩展支持。

现在,Qsys可以在FPGA架构中生成业界标准AMBA AHB和APB总线接口。而且,这些接口符合ARM的TrustZone要求,支持客户在安全的关键系统资源和其他非安全系统资源之间划分整个基于SoC-FPGA的系统。

3、DSP Builder设计工具支持系统开发人员在DSP设计中高效的实现高性能定点和浮点算法。

新特性包括更多的math.h函数,提高了精度,增强了取整参数,为定点和浮点FFT提供可参数赋值的FFT模块,还有更高效的折叠功能,提高了资源共享能力。

Qiartus13.1常见问题

问题一:

USB Blaster连接上,电脑无任何反应,之前安装过驱动也能使用,于是卸载Quartus并重装,问题解决。

问题二:

在综合时,出现错误,说软件不支持全部的器件,明显是破解不完全。原来是破解步骤有误,做了修正。

问题三:

能下载程序,但是程序不工作,很可能是晶振的问题(晶振不接也可以正常下载程序的),以为是晶振虚焊什么的,最后发现是晶振引脚与芯片时钟之间一个电阻未连接。

Qiartus13.1更新日志

日日夜夜的劳作只为你可以更快乐

嘛咪嘛咪哄~bug通通不见了!

提取码: 6663

华军小编推荐:

在经历了那么多年的更新与优化,Qiartus13.1变得更加人性化,也更加的具有科技感,强烈推荐给大家,欢迎下载。感兴趣的还可以下载门窗CC厂家版、杜特门窗大师傅、vect2000矢量化软件、我家摆摆看、GeoCorelDRAW。

有用

有用

有用